Разница между архитектурой и микроархитектурой процессора?

Есть ли разница между терминами «архитектура» и «микроархитектура» процессора?

1 ответ 1

Обычно под «архитектурой» понимается архитектура уровня набора команд (Instruction Set Architecture, ISA).

Давайте вспомним, что главной задачей CPU является исполнение программ. Согласитесь, что нам не важно, как CPU работает внутри, важно что он исполняет программы, которые мы ему передаем. И не просто исполняет, а исполняет именно так, как мы задумали! Вопрос в том, какие программы может исполнять определенный процессор и какова семантика этих программ. Именно это и определяет ISA — какие программы CPU может исполнять и что эти программы делают, а вот микроархитектура определяет, как CPU устроен изнутри.

Теперь немного подробнее.

ISA — это интерфейс между CPU и программами, которые на этом CPU исполняются. ISA определяет количество регистров, которые видны программисту, доступные инструкции, правила выравнивания и так далее. Если вы хотите написать программу для конкретного CPU вы берете справочник по его ISA и пишите инструкции одна за другой. Таким справочником, например, является Intel® 64 and IA-32 Architectures Software Developer’s Manuals — в нем описывается программная модель архитектур Intel 64 и IA-32 (это архитектуры семейства x86, которые используются в большинстве современных десктопных компьютерах).

В свою очередь микроархитектура определяет то, как CPU устроен внутри. Из каких функциональных узлов он состоит, какая иерархия кэшей, как декодируются инструкции, сколько стадий в конвейере и так далее.

Микроархитектура, не влияет на семантику и результат исполнения программ, но влияет на скорость их исполнения. Мы можем запустить Doom 3 как на старом Pentim IV, так и на новеньком Threadripper — и там и там он будет работать, вот только скорость работы на последнем CPU будет выше.

Кроме производительности микроархитектура влияет на энергопотребление процессора. Например, в свое время Intel запустила линейку процессоров Atom, которая была нацелена на мобильные устройства. Эти CPU реализовали ту же архитектуру x86, но их внутреннее устройство позволяло экономить потребление энергии, что делало возможным их использование в переносимых устройствах.

В принципе, об этом можно говорить долго, но в целом ISA и микроархитектура — это разные уровни абстракции. Если рассматривать CPU как черный ящик, то ISA — это его интерфейс, а микроархитектура — внутреннее устройство.

† Это, конечно, не совсем так. Программист и компилятор могут использовать свои знания о микроархитектуре конкретного процессора для применения определенных низкоуровневых оптимизаций: зная размер кэша можно разместить код и данные так, чтобы они влезали в кэш-линию, зная что конкретный процессор поддерживает delay slot компилятор может использовать эту информацию, чтобы, например, нивелировать задержку ветвления и так далее.

‡ Сильное и не совсем корректное упрощение. Хотя, конечно, иногда и приходится беспокоиться о memory barriers, но в целом программа действительно исполняется последовательно для программиста.

* Если кто-то знаком с C++, это что-то типа as if rule.

Собственная платформа. Часть 0.1 Теория. Немного о процессорах

Здравствуй, мир! Сегодня у нас серия статьей для людей со средними знаниями о работе процессора в которой мы будем разбираться с процессорными архитектурами (у меня спелл чекер ругается на слово Архитектурами/Архитектур, надеюсь я пишу слово правильно), создавать собственную архитектуру процессора и многое другое.

Принимаются любые замечания!

Немного про архитектуру процессора

Исторически сложилось, что существуют много процессоров и много архитектур. Но многие архитектуры имеют схожести. Специально для этого появились «Группы» архитектур типа RISC, CISC, MISC, OISC (URISC). Кроме того они могут иметь разные архитектуры адресации памяти (фон Неймана, Гарвард). У каждого процессора есть своя архитектура. Например большинство современных архитектур это RISC (ARM, MIPS, OpenRISC, RISC-V, AVR, PIC** и т.д.), но есть архитектуры которые выиграли просто за счет других факторов (Например удобство/цена/популярность/etc) Среди которых x86, x86-64 (Стоит отметить, что x86-64 и x86 в последних процессорах используют микрокод и внутри них стоит RISC ядро), M68K. В чем же их отличие?

Reduced Instruction Set Computer — Архитектура с уменьшенным временем выполнения инструкций (из расшифровка RISC можно подумать, что это уменьшенное количество инструкций, но это не так). Данное направления развилось в итоге после того, как оказалось, что большинство компиляторов того времени не использовали все инструкции и разработчики процессоров решили получить больше производительности использую Конвейеры. В целом RISC является золотой серединой между всеми архитектурами.

Яркие примеры данной архитектуры: ARM, MIPS, OpenRISC, RISC-V

Что такое TTA? ТТА это Архитектура на основе всего одной инструкции перемещения из одного адреса памяти в другую. Данный вариант усложняет работу компилятора зато дает большую производительность. У данной архитектуры есть единственный недостаток: Сильная зависимость от шины данных. Именно это и стало причиной ее меньшей популярности. Надо отметить что TTA является разновидностью OISC.

Яркие примеры: MOVE Project

OISC (URISC)?

One Instruction Set Computer — Архитектура с единственной инструкцией. Например SUBLEQ. Такие архитектуры часто имеют вид: Сделать действие и в зависимости от результата сделать прыжок или продолжить исполнение. Зачастую ее реализация достаточно простая, производительность маленькая, при этом снова ограничение шиной данных.

Яркие примеры: BitBitJump, ByteByteJump, SUBLEQ тысячи их!

CISC — Complex Instruction Set Computer — ее особенность в увеличенных количествах действий за инструкцию. Таким образом можно было теоретически увеличить производительность программ за счет увеличения сложности компилятора. Но по факту у CISC плохо были реализованы некоторые инструкции т.к. они редко использовались, и повышение производительности не было достигнуто. Особенностью этой группы является еще ОГРОМНАЯ Разница между архитектурами. И несмотря на названия были архитектуры с маленьким количеством инструкций.

Яркие примеры: x86, M68K

Адресация памяти

Архитектура фон Неймана

Особенностью таких архитектур была общая шина данных и инструкций. Большинство современных архитектур это программный фон Нейман, однако никто не запрещает делать аппаратный Гарвард. У данной архитектуры большим недостатком является большое зависимости производительности процессора от шины. (Что ограничивает общую производительность процессора).

Архитектура гарварда

Особенность этой архитектуры является отдельная шина данных и инструкций. Дает большую производительность чем фон Нейман за счет возможности за один такт использовать обе шины (читать из шины инструкций и одновременно записывать в шинну данных), но осложняет архитектуру и имеет некоторые ограничения. В основном используется в микроконтроллерах.

Особенности процессоров

Конвейеры

Что такое конвейеры? Если сказать очень глупым языком это несколько параллельных действий за один такт. Это очень грубо, но при этом отображает суть. Конвейеры за счет усложнения архитектуры позволяют поднять производительность. Например конвейер позволяет прочитать инструкцию, исполнить предыдущую и записать в шину данных одновременно.

На картинке более понятно, не правда?

IF — получение инструкции,

ID — расшифровка инструкции,

EX — выполнение,

MEM — доступ к памяти,

WB — запись в регистр.

Вроде все просто? А вот и нет! Проблема в том что например прыжок (jmp/branch/etc) заставляют конвейер начать исполнение (получение след. инструкции) заново таким образом вызывая задержку в 2-4 такта перед исполнение следующей инструкции.

Расширение существующих архитектур

Достаточно популярной техникой является добавление в уже существующую архитектуру больше инструкций через расширения. Ярким примером является SSE под x86. Этим же грешит ARM и MIPS и практически все. Почему? Потому что нельзя создать унивирсальную архитектуру.

Другим вариантом является использование других архитектур для уменьшения размера инструкций.

Яркий пример: ARM со своим Thumb, MIPS с MIPS16.

Техники применяемые в GPU

В видеокартах часто встречается много ядер и из-за этой особенности появилась потребность в дополнительных решениях. Если конвейеры можно встретить даже в микроконтроллерах то решения используемых в GPU встречаются редко. Например Masked Execution (Встречается в инструкциях ARM, но не в Thumb-I/II). Еще есть другие особенность: это уклон в сторону Floating Number (Числа с плавающей запятой), Уменьшение производительности в противовес большего количества ядер и т.д.

Masked Execution

Данный режим отличается от классических тем, что инструкции исполняются последовательно без использования прыжков. В инструкции хранится некоторое количество информации о том при каких условия эта инструкция будет исполнена и если условие не соблюдено то инструкция пропускается.

Ответ прост! Что бы не нагружать шину инструкций. Например в видеокартах можно загрузить тысячи ядер одной инструкцией. А если бы использовалась система прыжков то пришлось бы для каждого ядра ждать инструкцию из медленной памяти. Кеш частично решает проблему, но все еще не решает проблему полностью.

Прочее

Здесь мы будем описывать несколько техник используемых в центральный процессорах и микроконтроллерах.

Прерывания

Прерывания это техника при которой исполняемый в данный момент код приостанавливается для выполнения какой-то другой задачи при каких-то условиях. Например при доступе в несуществующий участок памяти вызывается HardFault или MemoryFault прерывания или исключения. Или например если таймер отсчитал до нуля. Это позволяет не бездействовать пока нужно ждать какое-то событие.

Какие недостатки? Вызов прерывания это несколько тактов простоя и несколько при возврате из прерывания. Так же несколько инструкций в начале кода будет занято инструкциями для Таблицы прерываний.

Exception (исключения)

Но кроме прерываний еще существуют исключений которые возникают например при деления на ноль. Зачастую его совмещают с прерываниями и системными вызовами, как например в MIPS. Исключения не всегда присутствуют в процессоре например как в AVR или младших PIC

Системные вызовы

Системные вызовы используется в Операционных системах для того, чтобы программы могли общаться с операционной системой например просить ОС прочитать файл. Очень похоже на прерывания. Аналогично исключениям не всегда присутствуют в процессоре

Контроллеры доступа в память и прочие методы сдерживания программ

Здесь описываются методы запрета доступа приложений к аппаратуре напрямую.

Привилегированный режим

Это режим в котором стартует процессор. В таком режиме программа или ОС имеют полный доступ к памяти в обход MMU/MPU. Все программы запускаются в непривилегированном режиме во избежания прямого доступа к аппаратным подсистемам программ для этого не предназначенных. Например вредоносным программам. В Windows ее часто называют Ring-0, а в *nix — системным. Не стоит путать Привелигированный пользователь и Привилегированный режим ибо в руте вы все еще не можете иметь прямой доступ к аппаратуре (можно загрузить системный модуль который позволит это сделать, но об этом чуть позже 🙂

MPU и MMU

MPU и MMU используется в современных системах чтобы изолировать несколько приложений. НО если MMU позволяет «передвинуть» память то MPU позволяет только блокировать доступ к памяти/запуск кода в памяти.

PIC (PIE)

Что такое PIE? (PIC не использую для избежания путаницы с МК PIC). PIE это техника благодаря которой компилятор генерирует код который будет работать в любом месте в памяти. Эта техника в совмещении с MPU позволяет компилировать высокие языки программирования которые будут работать и с MPU.

Популярная техника SIMD используется для того, что бы за один такт выполнять несколько действий над несколькими регистрами. Иногда бывают в качестве дополнений к основной архитектуре, например, как в MIPS, ARM со своими NEON/VFP/etc, x86 со своим SSE2.

Reposition for Optimization

Это техника Используется для оптимизации кода, генерируемого компилятором, с помощью пересортировки инструкций, увеличивая производительность процессора. Это позволяет использовать конвейер на полную.

Status register

Что такое регистр статуса? Это регистр который хранит состояние процессора. Например находится ли процессор в привилегированном режиме, чем закончилась операция последнего сравнения.

Используется в связке с Masked Execution. Некоторые разработчики специально исключают регистр статуса ибо он может являться узким местом как поступили в MIPS.

В MIPS нет отдельной инструкции загрузки константы в память, но есть инструкция addi и ori которая позволяет в связке с нулевым регистром ($0) эмулировать работу загрузки константы в регистр. В других архитектурах она присутствует. Я затронул эту тему, потому что она пригодиться нам в статьях с практикой.

Rd, Rs vs Rd, rs, rt

Идут множество споров насчет того сколько должно быть операндов в арифметических инструкциях. Например в MIPS используется вариант с 3-мя регистрами. 2 операнда, 1 регистр записи. С другой стороны, использование двух операндов позволяет сократить код за счет уменьшения размера инструкции. Пример совмещения является MIPS16 в MIPS и Thumb-I в ARM. В плане производительности они практически идентичны (Если исключать размер инструкции как фактор).

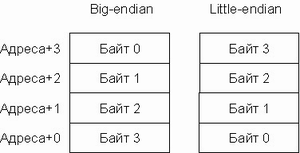

Endianness

Порядок байт. Возможно вам знакомы Выражения Big-Endian и Little-Endian. Они описывают порядок байт в инструкциях/в регистрах/в памяти/etc. Здесь думаю все просто :). Есть процессоры которые совмещают режимы, как MIPS, или которые используют одну систему команд, но имеют разный порядок байт, например ARM.

Битность процессора

Итак, что такое битность процессора? Многие считают, что это битность шины данных, но это не так. Почему? В ранние переоды микроконтроллеров и микропроцессоров шина могла быть, например, 4-х битной, но передавала пакетами по 8 бит. Для программы казалось, что это 8-и битный режим, но это была иллюзия, как и сейчас. Например, в ARM SoC-ах часто применяют 128-и битную шину данных или инструкций.

Сопроцессоры

Что такое сопроцессоры? Сопроцессоры являются элементами процессора или внешней микросхемой. Они позволяют исполнять инструкции, которые слишком громоздки для основной части процессора. Как яркий пример, сопроцессоры в MIPS для деления и умножения. Или например 387 для 80386, который добавлял поддержку чисел с плавающей запятой. А в MIPS сопроцессоров было много и они выполняли свои роли: контролировали прерывания, исключения и системные вызовы. Часто сопроцессоры имеют собственные инструкции и на системах, где этих инструкций нет, (пример ARM) эмулируют ее через Trap-ы (ловушки?). Несмотря на костыльность и маленькую производительность, они часто являются единственным выбором в микроконтроллерах.

Атомарность операций

Атомартность операций обеспечивает потоко-независимое исполнение за счет инструкций, которые выполняют несколько действий за один псевдотакт.

Вариант другого решения атомарность переферии. Например для установки ножки в STM32 в высокое и низкое состояние используется разные регистры, что позволяет иметь атомарность на уровне переферии.

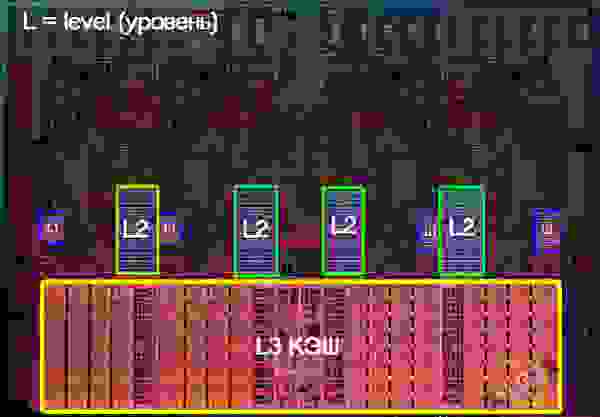

Вы, навярняка, слышали о L1, L2, L3 и регистрах. Если коротко, процессор анализирует часть кода, чтобы предугадать прыжки и доступ в память и зараннее просит кеш получить эти данные из памяти. Кеш зачастую бывает прозрачным для программы, но бывают и исключения из этого правила. Например, в программных ядрах в ПЛИС используется програмный кеш.

И вы кончено слышали о такой вещи, как Cache Miss или промах по кешу. Это операция которая не была предусмотрена процессорам или процессор не успел закешировать эту часть памяти. Что достаточно часто является проблемой замедления доступа к памяти. Промах проходит незаметно для программы, но не останутся незаметными просадки в производительности.Так же переключения контекстов например при прерываниях тоже заставляет страдать кеш ибо небольшой код сбивает конвейер и кеш для собственных нужд.

Shadow Registers

В современных процессорах часто используется техника теневых регистров. Они позволяют переключаться между прерываниями и пользовательским кодом практически без задержек связанных с сохранением регистров.

Stack

Спросите тогда что такое куча (Heap)? Куча это память размером намного больше чем стек (Стек обычно

1MB). В хипе храниться все глобальное. Например все указатели полученные с помощю Malloc указывают на часть куча. А указатели хранятся в стеке или в регистрах. С помощью инструкций загрузки данных относительно регистра можно ускорить работу стека и других доступов к памяти по типу стека, поскольку не нужно постоянно использовать операции PUSH/POP, INC/DEC или ADDI, SUBI (добавить константу), чтобы получить данные глубже по стеку, а можно просто использовать доступ относительно стека с отрицательным смещением.

Регистры

Не буду описывать регистры слишком подробно. Это мы затронем в практической статье.

В x86 регистров достаточно мало. В MIPS используется увеличенное количество регистров, а именно 31 ($0 имеет значение всегда равное нулю). В процессоре университета Беркли использовались регистровые окна, которые жестки ограничивали вложенность функций, при этом имея лучшую производительность. В других же, таких как AVR, ограничили использование регистров. Для примера: три 16-битных можно трактовать как шесть восьмибитных, где первые 16ть недоступны при некоторых операциях. Я считаю, что лучший метод был выбран MIPS-ом. Это мое сугубо личное мнение.

Выравнивание

Что такое выравнивание? Оставлю-ка я этот вопрос вам 🙂

Конец

Это конец первой главы нулевой части. Вся серия будет крутиться вокруг темы создания собственного процессора. Собственной операционной системы. Собственного ассемблера. Собственного компилятора и много чего другого.

Национальная библиотека им. Н. Э. Баумана

Bauman National Library

Персональные инструменты

Микроархитектура

В компьютерной инженерии микроархитектура (англ. microarchitecture; иногда сокращается до «µarch» или «uarch» ), также называемая организация компьютера — это способ, которым данная архитектура набора команд (ISA, АНК) реализована в процессоре. Каждая АНК может быть реализована с помощью различных микроархитектур. Реализации могут варьироваться в зависимости от целей конкретной разработки или в результате технологических сдвигов. Архитектура компьютера является комбинацией микроархитектуры, микрокода и АНК.

Содержание

Аспекты микроархитектуры

Конвейерный тракт данных является наиболее широко используемым в современных микроархитектурах. Эта техника используется в большинстве современных микропроцессоров, микроконтроллеров и цифровых сигнальных процессоров. Конвейерная архитектура позволяет нескольким инструкциям перекрываться в исполнении, что напоминает сборочную линию. Конвейер включает несколько различных стадий, выбор которых является фундаментальным при разработке микроархитектуры. [1] Некоторые из этих стадий включают выбор инструкций, декодирование инструкций, исполнение и запись результата. Некоторые архитектуры включают другие стадии, такие как доступ к памяти. Дизайн конвейера — один из центральных вопросов проектирования микроархитектуры.

Устройства исполнения также являются ключевыми для микроархитектуры. Они включают арифметико-логические устройства, устройства обработки чисел с плавающей точкой, устройства выборки и хранения, прогнозирование ветвления, параллелизм на уровне данных (SIMD). Эти блоки производят операции или вычисления процессора. Выбор числа блоков исполнения, их задержек, пропускной способности и способа соединения памяти с системой также являются микроархитектурными решениями.

Проектные решения уровня системы, такие как включать или нет периферийные устройства типа контроллеров памяти, могут считаться частью процесса разработки микроархитектуры, поскольку они содержат решения по уровню производительности и способам соединения этих периферийных устройств.

В отличие от архитектурного дизайна, где достижение определённого уровня производительности является главной целью, проектирование микроархитектуры уделяет большее внимание другим ограничениям. Поскольку дизайн микроархитектуры прямо влияет на то, что происходит в системе, внимание должно быть уделено следующим проблемам:

Связь с микрокодом и архитектурой набора команд

АНК — это приблизительно то же самое, что и модель программирования, с точки зрения программиста на языке ассемблера или создателя компилятора. АНК, в числе прочего, включает модель исполнения, регистры процессора, форматы адресов и данных, в то время, как микроархитектура включает составные части процессора и способы их взаимосвязи и взаимодействия для реализации АНК.

Однако во многих случаях работа элементов микроархитектуры контролируется микрокодом, встроенным в процессор. В случае наличия слоя микрокода в архитектуре процессора он выступает своеобразным интерпретатором, преобразуя команды уровня АНК в команды уровня микроархитектуры. При этом различные системы команд могут быть реализованы на базе одной микроархитектуры. [2]

Машины с различной микроархитектурой могут иметь одинаковую АНК и, таким образом, быть пригодными для выполнения тех же программ. Новые микроархитектуры и/или схемотехнические решения вместе с прогрессом в полупроводниковой промышленности являются тем, что позволяет новым поколениям процессоров достигать более высокой производительности, используя ту же АНК.

Концепции микроархитектуры

В общем случае, все ЦПУ, одночиповые микропроцессоры и многочиповые реализации выполняют программы, производя следующие шаги: Чтение инструкции и её декодирование Поиск всех связанных данных, необходимых для обработки инструкции Обработка инструкции Запись результатов Эта последовательность выглядит просто, но осложняется тем фактом, что иерархия памяти (где располагаются инструкции и данные), которая включает в себя кэш, основную память и энергонезависимые устройства хранения, такие как жёсткие диски, всегда была медленнее самого процессора. Шаг (2) часто привносит длительные (по меркам ЦПУ) задержки, пока данные поступают по компьютерной шине. Значительная часть исследований посвящена разработкам, которые позволяют избегать таких задержек, насколько это возможно. В течение многих лет главной целью было выполнять больше инструкций параллельно, увеличивая таким образом эффективную скорость выполнения программ. Эти усилия вызывают усложнение логики и структуры схем. Изначально эти техники могли быть реализованы только на дорогих мейнфреймах и суперкомпьютерах вследствие большого объёма схем, необходимого для этого. По мере того, как полупроводниковая промышленность развивалась, всё большее количество этих техник могло быть реализовано в единственном полупроводниковом чипе. Краткий обзор микроархитектурных концепций, распространённых в современных процессорах.

Выбор системы команд

Однако выбор системы команд в значительной степени определяет сложность реализации высокопроизводительных устройств. Известной стратегией, использовавшейся при разработке первых RISC-процессоров, было упрощение инструкций до минимума индивидуальной семантической сложности в сочетании с высокой упорядоченностью и простотой кодирования. Такие единообразные инструкции просто извлекались, декодировались и исполнялись конвейерообразным манером, позволяя реализовывать простую стратегию сокращения числа логических уровней для достижения более высоких частот функционирования. При этом кэш-память инструкций компенсировала естественно низкую плотность кода при высоких частотах работы, а большие наборы регистров использовались для исключения, насколько это возможно, обращений к (медленной) памяти.

Конвейеризация инструкций

Одна из первых и наиболее мощных техник повышения производительности — это использование конвейера инструкций. Ранние модели процессоров должны были выполнить все описанные выше шаги для одной инструкции, прежде чем перейти к следующей. Большие части схемы оставались неиспользуемыми на любом отдельном шаге. Например, часть схемы, осуществляющая декодирование инструкции, останется неиспользуемой во время её исполнения и т. д.

Конвейеры увеличивают производительность, позволяя нескольким инструкциям прокладывать свой путь через процессор в одно и то же время. В том же простом примере процессор начал бы декодировать (шаг 1) новую инструкцию, в то время как предыдущая ожидала бы результатов. В этом случае до четырёх инструкций могло находиться в обработке единовременно, позволяя процессору выглядеть в четыре раза быстрее. В то же время, любая отдельная инструкция выполняется в течение того же самого времени, поскольку существуют те же четыре шага, хотя в целом процессор выдаёт больше обработанных инструкций и может работать на значительно более высоких тактовых частотах.

RISC сделал конвейеры меньше и значительно проще в конструировании, отделив каждый этап обработки инструкций, зафиксировав длину машинной инструкции и сделав время их выполнения одинаковым — один такт или как максимум один цикл доступа к памяти (из-за выделения инструкций load и store). Процессор в целом функционирует на манер сборочной линии с инструкциями, поступающими с одной стороны и результатами, выходящими с другой. Из-за уменьшенной сложности классического RISC-конвейера, конвейерезированное ядро и кэш инструкций могли быть размещены на кристалле того же размера, который содержал бы лишь ядро в случае CISC архитектуры. Это и было истинной причиной того, что RISC был быстрее. Ранние разработки, такие как SPARC и MIPS часто работали в 10 раз быстрее CISC решений Intel и Motorola той же тактовой частоты и цены.

Конвейеры никоим образом не ограничиваются RISC разработками. В 1986 году флагманская реализация VAX (VAX 8800) была сильно конвейеризирована, несколько опережая коммерческие реализации MIPS и SPARC. Большинство современных процессоров (даже встроенных) конвейеризированы, а процессоры с микрокодом но без конвейеров можно встретить только среди наиболее ограниченных по площади встроенных решений. Большие CISC машины, от VAX 8800 до современных Pentium 4 и Athlon используют как микрокод, так и конвейеры. Улучшения в конвейеризации и кэшировании — два важнейших микроархитектурных сдвига, позволяющих производительности процессоров идти в ногу со схемными технологиями, на которых они основаны.

Когда улучшения в производстве чипов позволили размещать на кристалле ещё больше логики, начался поиск способов применения этого ресурса. Одним из направлений стало размещение прямо на кристалле чипа очень быстрой кэш памяти, доступ к которой происходил всего за несколько тактов процессора, в отличие от большого их количества при работе с основной памятью. При этом процессор также включал контроллер кэша, автоматизировавший чтение и запись данных в кэш.

RISC процессоры стали снабжаться кэшем в середине-конце 1980-х (часто объёмом всего 4 КБ). Этот объём постоянно возрастал, и современные процессоры имеют по крайней мере 512 КБ, а наиболее мощные 1,2,4,6,8 и даже 12 МБ кэш памяти, организованной в иерархию. В целом, больший объём кэша означает большую производительность вследствие меньшего времени простоя процессора.

Кэш память и конвейеры хорошо дополняют друг друга. Если первоначально не имело смысл создавать конвейеры, работающие быстрее времени доступа к основной памяти, то с появлением кэша конвейер стал ограничен лишь более короткими задержками доступа к быстрой памяти на чипе. В итоге это позволяло увеличивать тактовые частоты процессоров.

Прогнозирование ветвления

Одно из препятствий в достижении более высокой производительности за счёт параллелизма на уровне данных возникает вследствие остановки и переполнения конвейера при ветвлениях. Обычно до конца неизвестно, будет ли выбрана ветвь условного ветвления в конвейере, поскольку ветвление зависит от результата, который берётся из регистра. С того времени, как декодер инструкций процессора выяснил, что натолкнулся на инструкцию, вызывающую ветвление до того, как определяющее решение значение может быть прочитано из регистра, конвейер необходимо остановить на несколько циклов. Если ветвь выбрана, то его нужно заполнить. Одновременно с ростом частоты процессоров увеличивалась глубина конвейеров и современные разработки имеют до 20 стадий. С учётом того, что в среднем каждая пятая инструкция вызывает ветвление, без дополнительных мер возникнет значительный простой.

Такие техники, как прогнозирование ветвлений и спекулятивное исполнение используются для уменьшения этих потерь.

Прогнозирование ветвления заключается в том, что оборудование делает обоснованное решение о том, какая из ветвей будет выбрана для исполнения. Современные разработки имеют достаточно сложные статистические системы прогнозирования, которые используют результаты последних ветвлений для предсказания будущих с большой точностью. Такие решения позволяют аппаратуре предварительно считать инструкции, не дожидаясь результата из регистра.

Спекулятивное исполнение — это дальнейшее развитие идеи, при котором инструкции из предсказанного пути не только считываются, но и исполняются до того, как становится точно известно, будет ли выбрана ветвь. Это помогает достичь высокой производительности, если решение было правильным, но вызывает риск большой потери времени, если решение ошибочно и инструкции нужно отменить.

Суперскалярность

Изначально, даже процессоры конвейерной микроархитектуры могли запускать только одну инструкцию в каждый момент времени. Очевидно, что программы могли бы выполняться быстрее, если запускать несколько инструкций одновременно. Именно этого достигают суперскалярные микроархитектуры за счёт использования нескольких одинаковых функциональных блоков, таких как АЛУ. Такие архитектуры появились когда на схеме стало возможно размещать больше элементов и к концу 1980-х они вышли на рынок.

В современных разработках часто можно видеть два устройства выборки, одно устройство хранения (многие инструкции не имеют результатов для хранения), два или более целочисленных АЛУ, два или более устройства обработки чисел с плавающей точкой, устройство SIMD и другие. Логика управления значительно усложнилась, обеспечивая чтение из памяти большого количества инструкций, распределение их по свободным функциональным блокам, сбор и упорядочение результатов.

Внеочередное исполнение

Появление кэшей сократило частоту и длительность простоев из-за ожидания чтения данных из иерархии памяти, но не устранило их совсем. В ранних разработках отсутствие данных в кэше вынуждало контроллер кэша остановить процессор и ожидать. Очевидно, что в программе почти всегда есть другие инструкции, данные для которых доступны в кэше в данный момент. Внеочередное исполнение позволяет выполнить эти инструкции в то время, как предыдущие ожидают данных из кэша. Затем результаты упорядочиваются так, что сохраняется предусмотренный в программе порядок. Эта техника также используется, чтобы избегать других остановок вследствие зависимых операндов, как в случае инструкций, ожидающих результатов длинных операций с плавающей точкой или других многоцикловых операций.

Переименование регистров

Переименование регистров — это техника, позволяющая избежать ненужного последовательного выполнения инструкций программы вследствие использования этими инструкциями одних и тех же регистров. Положим имеется две группы инструкций, использующих один регистр. Одна группа инструкций должна предшествовать другой для того, чтобы освободить этот регистр. Но если вторую группу инструкций перенаправить на другой однотипный регистр, то обе группы могут выполняться параллельно.

Многопроцессорность и многопоточность

В определённый период разработчики компьютеров оказались в тупике, связанном с растущим несоответствием между рабочими частотами ЦПУ и временем доступа к DRAM. Ни одна из технологий, эксплуатирующих параллелизм уровня инструкций внутри одной программы не могла компенсировать длительные остановки, возникающие когда данные должны быть прочитаны из основной памяти. К тому же, большое число транзисторов и высокие тактовые частоты, необходимые для более совершенных способов организации параллелизма инструкций, требовали таких уровней рассеивания тепла, что устройства нельзя было дёшево охлаждать. По этим причинам новые поколения компьютеров стали использовать более высокие уровни параллелизма, существовавшие вне одной программы или одного программного потока.

Эта тенденция также известна как производительные вычисления (throughput computing) и возникла в своё время на рынке мэйнфреймов, где OLTP требовала не столько высокой скорости обработки отдельной транзакции, сколько возможности обрабатывать большое их число одновременно. С распространением приложений, базирующихся на использовании транзакций, таких, как сетевая маршрутизация и обслуживание веб-сайтов, в компьютерной индустрии вновь появился акцент на ёмкости и пропускной способности.

Одним из способов достижения параллелизма такого вида являются многопроцессорные системы — компьютеры с несколькими ЦПУ. Когда-то ограничивавшиеся мэйнфреймами и суперкомпьютерами, многопроцессорные системы в виде миниатюрных (2-8)-процессорных серверов становятся обычным явлением в малом бизнесе. Для крупных корпораций характерны масштабные мультипроцессоры (16-256). В 1990-е появились и многопроцессорные персональные компьютеры.

По мере дальнейшего уменьшения размера транзисторов (с соответствующим увеличением их числа в интегральных микросхемах) получали распространение многоядерные процессоры, у которых несколько физических процессорных ядер размещаются в единственном кремниевом чипе. Сначала такие решения предназначались для рынка встроенных систем, где более простые и компактные архитектуры позволяли разместить несколько экземпляров ЦПУ на одном кристалле. К 2005 году полупроводниковая технология позволила поместить в один корпус два высокопроизводительных универсальных процессора. В некоторых проектах, таких, как UltraSPARC T1 Sun Microsystems, разработчики вернулись к более простым микроархитектурам (скалярным с исполнением по порядку) с тем, чтобы разместить больше процессоров на одном кристалле.

Многопоточность является ещё одной технологией, получившей распространение сравнительно недавно. Суть её в том, что когда процессору необходимо получить данные из медленной основной памяти, он вместо того, чтобы простаивать в ожидании этих данных, переключается на выполнение другого программного потока, который готов к исполнению. Не улучшая время выполнения отдельной программы, многопоточность тем не менее увеличивает пропускную способность всей системы. Концептуально операции многопоточного процессора эквивалентны переключению контекста (процесса или потока) на уровне операционной системы. Различие состоит в том, что многопоточный процессор производит переключение активного потока за один такт, в то время как программная реализация на уровне ОС требует на несколько порядков больших временных затрат. Это достигается путём аппаратной репликации регистрового контекста для каждого потока.

Дальнейшее развитие микроархитектур в этом направлении связано с одновременной многопоточностью. При этом суперскалярный процессор выполняет инструкции разных программ и потоков одновременно.